# 高周波におけるプローブピンのインダクタンス測定 -微小電子部品の電気特性評価に関する研究-

石松賢治\*·宮川隆二\*·木村佳\*\*

\* 電子部、\*\* 理化電子(株)

Probe Pin Inductance Measurement at High Frequencies - Study on Electric Characteristic of Small Size Parts -

Kenji ISHIMATSU\*, Ryuji MIYAGAWA\* and Kei KIMURA\*\*

半導体テストで使用する IC ソケットのプローブピンのインダクタンスとキャパシタンスを、1GHz から 10GHz の広い周波数帯域(GHz 帯)で測定した。基本的な測定方法として、ネットワークアナライザを用いて反射波の位相量を測定する方法 $^{1)}$  (以下 NA 法と略する)、時間領域反射法(以下 TDR 法と略する)がある $^{2)}$ 。この2つの方法でプローブピンを測定し、インダクタンスとキャパシタンスを抽出した。その結果は、インダクタンスとキャパシタンスはほぼ同じ値であり、測定方法の妥当性を確認できた。

### 1. はじめに

大容量かつ高速のデータ転送の需要の高まりから、今後、半導体チップ間の伝送速度は166Mビット/秒から2.5Gビット/秒と10倍以上に高速化される<sup>3)</sup>。県内には、半導体検査装置やその部品を製造する企業が多数ある。それら企業にとって、新製品開発や製品の品質を保証するために、高周波での評価が必要不可欠になっている。実際に、ICソケットのプローブピンを製造する県内企業より、プローブピンのインダクタンスとキャパシタンスを、1GHzから10GHzの高周波範囲(GHz帯)で、測定する要望があった。しかし、電子部品のインダクタンスやキャパシタンス測定では、これまでは、LCRメータが使われていたが、周波数1GHzまでしか測定できない。そこで、GHz帯でのプローブピンの測定方法を検討した。

半導体パッケージの高周波測定法 <sup>4</sup>があり、プローブピンの高周波測定法として、この測定法を参考にした。高周波での測定法は、NA 法と TDR 法がある。今回、この2つの測定法を使い、プローブピンのインダクタンス値とキャパシタンス値を抽出した。それらの値を比較することにより、高周波での測定方法の妥当性を確認した。

2. 理論

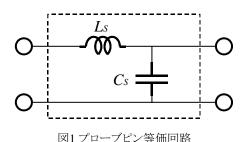

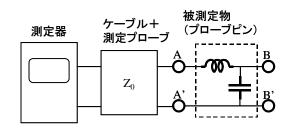

図1に最も簡単なプローブピンの等価回路を示す。この図の中で、Lsはインダクタンスであり、 $C_s$ はキャパシタンスである。図2にプローブピンを測定するための構成を示す。測定プローブをケーブルを使って、測定器と被測定物に接続する。ケーブルと測定プローブの特性インピーダンス $Z_s$ は、 $50\Omega$ である。

図2プローブピン測定の構成

## 2.1 NA 法

NA 法における、インダクタンスの測定法を示す。図 2 の測定構成図で、測定器としてネットワークアナライザを使用し、被測定物の終端(B-B)をショートする。ネットワークアナライザを使って、入射波を被測定物に加えて、入射波と反射波の位相差  $\theta$  を測定する。位相差は、式(1)に示すようにインダクタンスにより変わる。

$$\theta = \tan^{-1}(\frac{2 \cdot Z_0 \cdot \omega Ls}{\omega^2 Ls^2 - Z_0^2}) \qquad \cdots (1)$$

キャパシタンス測定では、被測定物の B-B'をオープン にし、その反射波の位相差を測定する。。 位相差は、式 (2)に示すように、キャパシタンス C。により変化する。

$$\theta = \tan^{-1}\left(\frac{2 \cdot Z_0 \cdot \omega \cdot C_s}{Z_0^2 \cdot \omega^2 \cdot C_s^2 - 1}\right) \qquad \cdots (2)$$

#### 2.2 TDR 法

TDR 法は、図2に示す構成で測定する。測定器は、

TDR オシロスコープを使う。TDR オシロスコープは、立ち上がり時間の短いステップ信号を発振し、その反射を時間領域で観測する。

インダクタンス測定では、図 2 に示す A-A '端子を ショートし、次に被測定物を接続し B-B'端子をショ

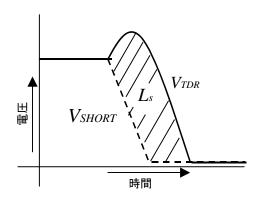

$$L_{s}=rac{Z_{0}}{2\cdot V_{IN}}\int\limits_{0}^{\infty}(V_{TDR}-V_{SHORT})dt$$

$Z_{0}$  特性インピーダンス

$V_{\mathrm{IN}}$  TDR電圧値

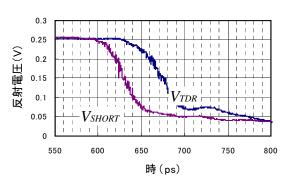

図3 TDR法によるインダクタンスの計算方法

ートして、反射波形を観測する。図 3 に示す  $V_{SHORT}$  は A-A'端子をショートしたときの波形であり、 $V_{TDR}$  は B-B'端子をショートしたときの波形である。 $V_{TDR}$ 波形と  $V_{SHORT}$  波形の差の合計がインダクタンスである。

キャパシタンス測定では、図 2 に示す A-A '端子を オープンにし、次に被測定物を接続し B-B'端子をオ

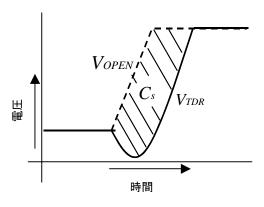

$$C_s = rac{1}{2 \cdot Z_0 \cdot V_{IN}} \int\limits_0^\infty (V_{TDR} - V_{OPEN}) dt$$

$Z_0$  特性インピーダンス

$V_{\mathrm{IN}}$  TDR電圧値

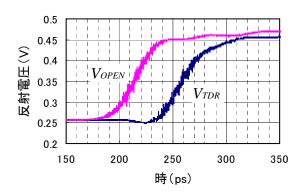

図4 TDR法によるキャパシタンスの計算方法

ープンにした時の反射波形が、図 4 の  $V_{OPEN}$  と  $V_{TDR}$  である。図 4 における  $V_{OPEN}$  波形と  $V_{TDR}$  波形の差の合計がキャパシタンスである。

## 3. 実験方法

## 3.1 プローブピンと測定用治具

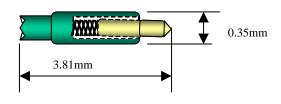

図5 測定するプローブピン

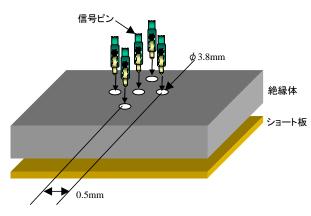

図6 測定用の治具

図 5 に測定するプローブピンを示す。プローブピンの実行長は3.81mm、直径は0.35mmである。図6に測定用の治具を示す。絶縁体は、IC ソケットと同じ材料を使い、厚みはプローブピンの実行長と同じ3.81mmである。この絶縁体に5つの穴を5mmピッチで開け、その穴にプローブピンを挿入する。真ん中のピンは測定するプローブピン(信号ピン)であり、周りのプローブピンは、GNDピンである。被測定物(プローブピン)の終端をショートするために、金メッキした銅板をショート板として使用した。被測定物の終端をオープンにするためには、絶縁板を用意した。

#### 3.2 測定プローブ

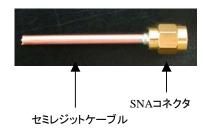

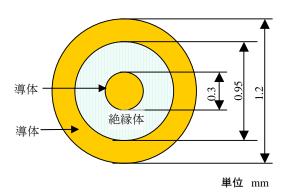

図7に測定プローブを示す。測定プローブは、同軸構造のセミレジットケーブルに SNA コネクタを付け、その片端をカットしたものを使った。このセミレジットと図 6 に示すプローブピンを挿入した絶縁材料にコンタクトさせる。セミレジットの心線は信号ピンと、セミレジットの外側の金属は 4本の GND ピント接続させる。

#### 3.3 測定器

NA 法では、測定器として、ネットワークアナライザ (アジレントテクノロジー 8720ES)を使用した。TDR 法では、 テクトロニクス社のオシロスコープ

(TDS8000)、また TDR 機能のオプションとして 80E04 を使用した。

(a) 測定プローブ

(a) 測定プローブ先端部断面

図7 測定プローブ

## 4. 実験結果

## 4.1 NA 法

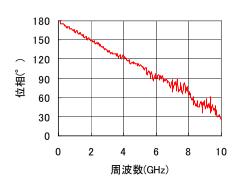

図8 NA測定結果(ショート)

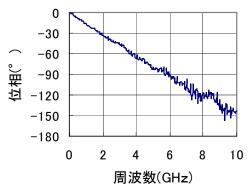

NA 法による測定結果を示す。図8 に終端をショートした場合の位相差を、図9 に終端をオープンした場合の位相差を示す。周波数が 5GHz 以下では、安定した測定結果が得られたが、それ以上の周波数で、測定値の変動が大きい。これはノイズの影響ではないかと思われる。

図9 NA測定結果(オープン)

図 8 から、プローブピンのインダクタンス値 1.11nH が得られた。図 9 から、キャパシタンス値は 0.44pF であった。

## 4.2 TDR 法

図10 TDR測定結果(ショート)

図11 TDR測定結果(オープン)

図 10 に被測定試料の終端をショートした場合の反射  $V_{TDR}$ 、 $V_{SHORT}$  波形を示す。図 10 から、590ps から 710ps の時間でインダクタンスを計算すると 0.95nH が得られた。710ps 以降は、反射波形が変動している。これは、絶縁体内のプローブピンの特性インピーダンスやプローブピンとショート板の間の接触抵抗などによる

多重反射が起こるためと思われる。

図 11 に被測定試料の終端をオープンした場合の反射波形  $V_{TDR}$ ,  $V_{OPEN}$ を示す。図 11 から、プローブピンのキャパシタンス値は 0.44pF であった。

#### 5. おわりに

NA法とTDR法で得られたプローブピンのインダクタンス値とキャパシタンス値を表1に示す。キャパシタンス値は同じであり、インダクタンス値もほぼ同じ値である。

|         | NA法    | TDR法    |

|---------|--------|---------|

| インダクタンス | 1.11nH | 0. 95nH |

| キャパシタンス | 0.44pF | 0. 44pF |

表1 プローブピン測定結果

プローブピンのキャパシタンス値、インダクタンス 値をNA法とTDR法の2つの測定方法から得た。その値 はほぼ等しく、今回の測定方法は、妥当であると考え られる。

今後は、プローブピンの高精度なインダクタンス値とキャパシタンス値を得るため、多重反射の影響を除いた解析方法を検討する。5)

#### 対 対

- "Package Inductance Measurement at High Frequencies", Proceedings of 42nd Electronic Components and Technology Conference, San Diego, CA, May 1992, pp 740-744

- 2) "TDR Techniques for Characterization and Modeling of Electronic Package", TDA Application Note PKGM-0703, 2001

- 3) "バスよりシリアル GHz 伝送への決断", 日経エレクトロニクス, No. 798, p101-127, 2001

- 4) "Guidelines for Measurement of Electronic Package Inductance and Capacitance Model Parameters", JEDEC Publication JEP-123, 1994

- 5) "Equivalent Circuit Modeling of Interconnects from Time-Domain Measurements", IEEE Transactions on Components, Vol. 16, No. 1, February 1993